易家知识网(易家电子)ejdz.cn

COPYRIGHT © 2023

渝ICP备20008086号-17

渝公网安备50010702505138号

渝公网安备50010702505138号

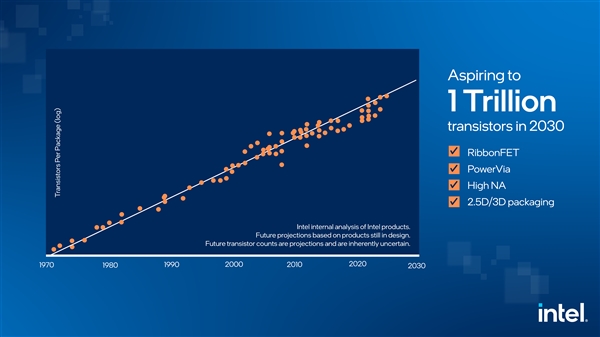

晶体管的数量/密度一直是衡量半导体技术进步的重要指标。目前单个芯片上可以实现超过1000亿个晶体管,比如Intel Ponte Vecchio GPU。在IEDM 2022 IEEE国际电子设备大会上,英特尔宣布了多项新的技术突破,并将继续执行已经诞生75年的摩尔定律。目标是到2030年在单个芯片上集成1万亿个晶体管,是现在的10倍。

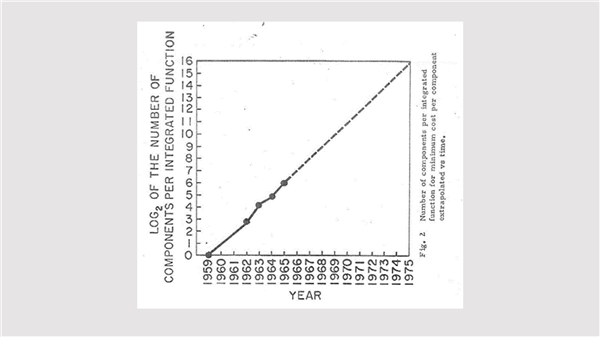

摩尔定律原型

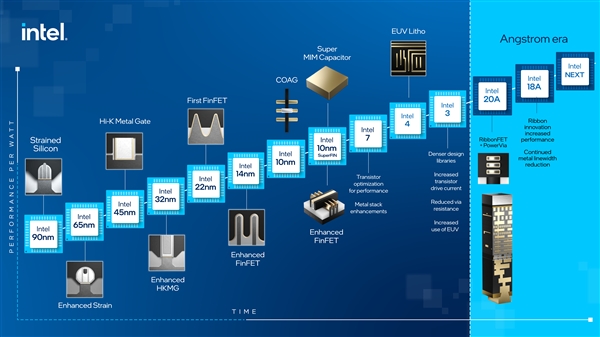

从应变硅、高K金属栅极、FinFET立体晶体管,到未来的RibbonFET GAA环绕栅极晶体管、PowerVia后置供电,再到2.5D EMIB+3D Foveros、Foveros Direct/Omni封装技术,Intel一直在从各项技术上推动摩尔定律。

IEDM 2022会议上,Intel披露了三个方面的技术突破:

1、下一代3D封装准单芯片

基于混合键合(hybrid bonding),将集成密度和性能再提升10倍。

同时,间距缩小到3微米,使得多芯片互连密度和带宽媲美如今的单芯片SoC。

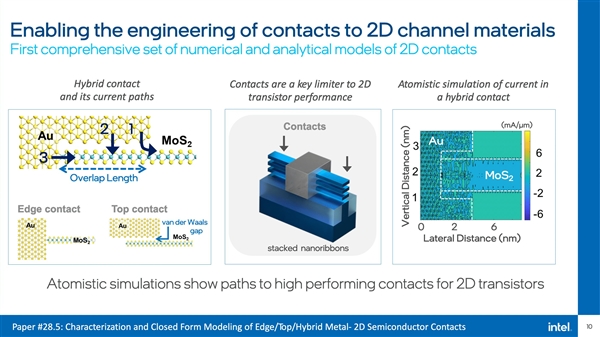

2、超薄2D材料在单芯片内集成更多晶体管

使用厚度仅仅3个原子的2D通道材料,Intel展示了GAA堆栈纳米片,在双栅极结构上,在室温环境、低漏电率下,达成了非常理想的晶体管开关速度。

第一次深入揭示了2D材料的电接触拓扑,可实现更高性能、更有弹性的晶体管通道。

3、高性能计算能效、内存新突破

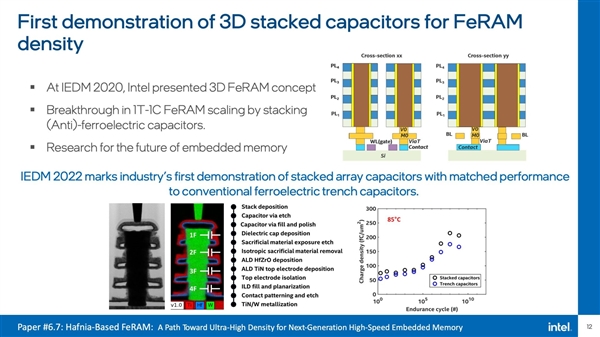

Intel研发了可垂直堆叠在晶体管之上的全新内存,并首次展示了全新的堆叠铁电电容,性能媲美传统铁电沟道电容,可用于在逻辑芯片上打造FeRAM。

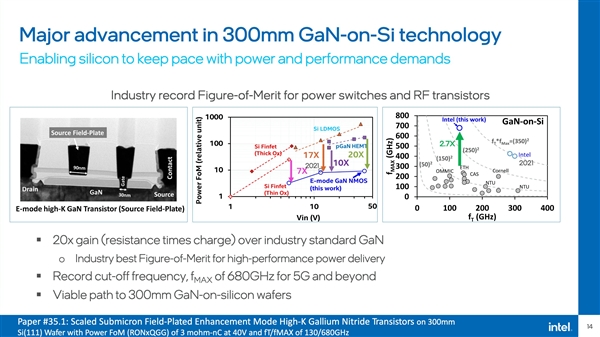

Intel正在打造300毫米直径的硅上氮化镓晶圆,比标准的氮化镓提升20倍。

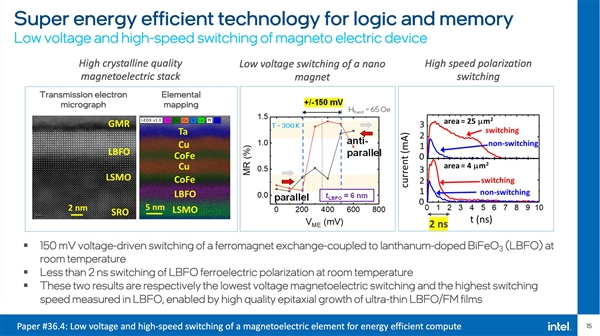

Intel在超高能效方面也取得了新的突破,尤其是晶体管在断电后也能保存数据,三道障碍已经突破两道,很快就能达成在室温下可靠运行。

Intel制造工艺路线图

暂无评论,期待你的妙语连珠

已收到!

我们将尽快处理。